FAIRCHILD

SEMICONDUCTOR

# CD4512BC 8-Channel Buffered Data Selector

## **General Description**

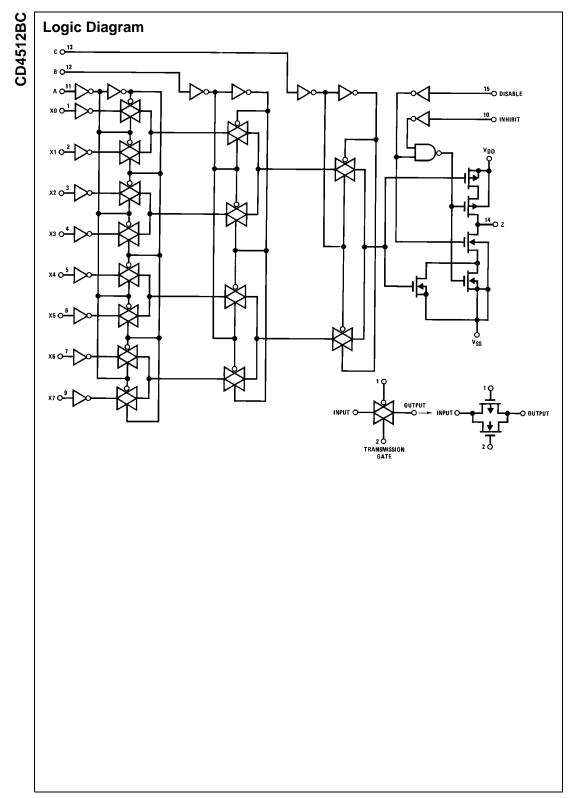

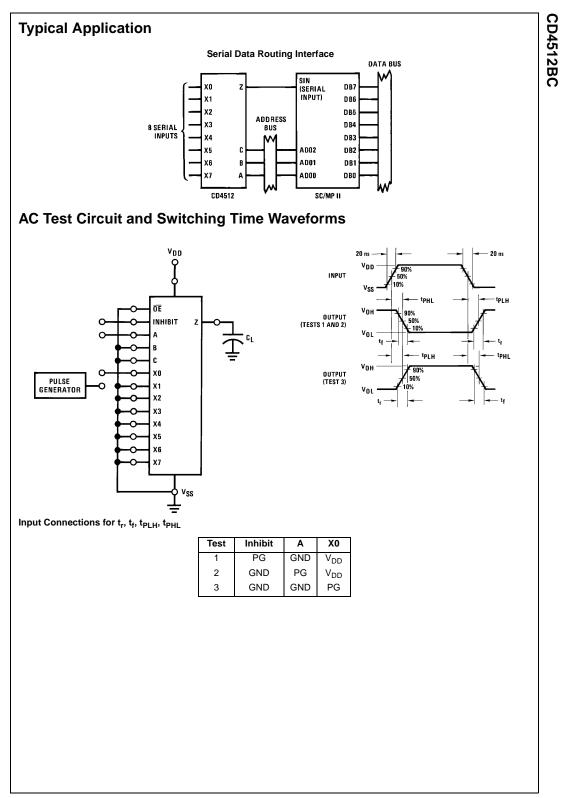

The CD4512BC buffered 8-channel data selector is a complementary MOS (CMOS) circuit constructed with N- and P-channel enhancement mode transistors. This data selector is primarily used as a digital signal multiplexer selecting 1 of 8 inputs and routing the signal to a 3-STATE output. A high level at the Inhibit input forces a low level at the output. A high level at the Output Enable ( $\overline{OE}$ ) inputs allow normal operation.

### **Features**

■ Wide supply voltage range: 3.0V to 15V

October 1987

Revised January 1999

- High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- 3-STATE output

- Low quiescent power dissipation: 0.25 µW/package (typ.) @ V<sub>CC</sub> = 5.0V

- Plug-in replacement for Motorola MC14512

## **Ordering Code:**

| Order Number                                                                                  | Package Number | r Package Description                                                             |  |  |  |

|-----------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------|--|--|--|

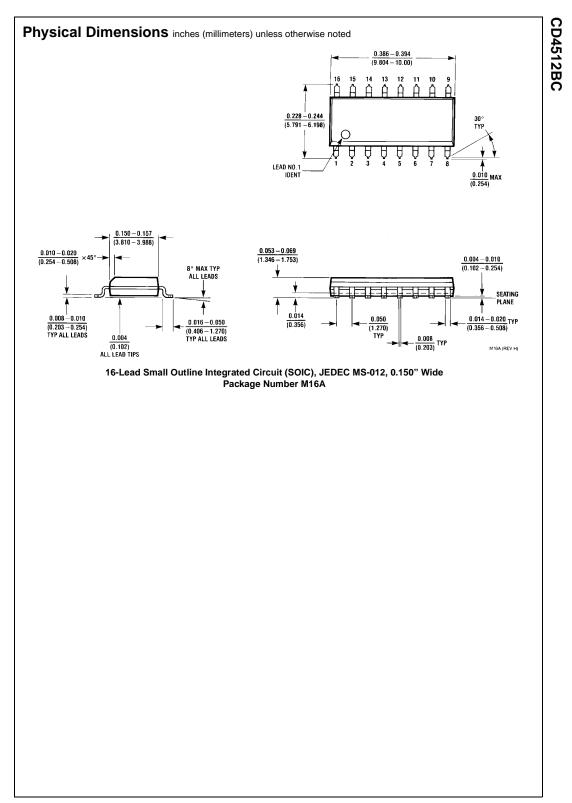

| CD4512BCM                                                                                     | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |  |  |  |

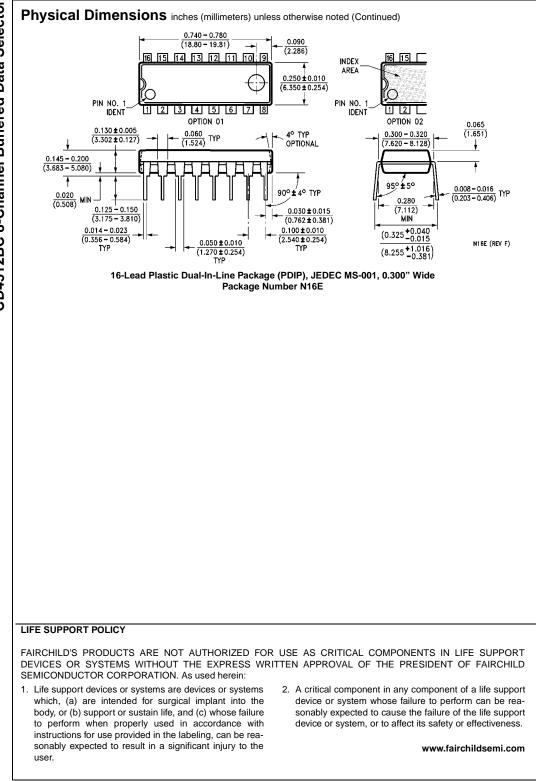

| CD4512BCN                                                                                     | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |  |  |  |

| Devices also available in Tane and Reel. Specify by appending suffix "X" to the ordering code |                |                                                                                   |  |  |  |

evices also available in Tape and Reel. Specify by appending suffix "X" to the ordering code.

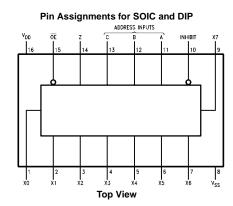

## **Connection Diagram**

## **Truth Table**

| Address Inputs |   |   | Control    | Output |      |  |

|----------------|---|---|------------|--------|------|--|

| С              | В | Α | Inhibit OE |        | z    |  |

| 0              | 0 | 0 | 0          | 0      | X0   |  |

| 0              | 0 | 1 | 0          | 0      | X1   |  |

| 0              | 1 | 0 | 0          | 0      | X2   |  |

| 0              | 1 | 1 | 0          | 0      | Х3   |  |

| 1              | 0 | 0 | 0          | 0      | X4   |  |

| 1              | 0 | 1 | 0          | 0      | X5   |  |

| 1              | 1 | 0 | 0          | 0      | X6   |  |

| 1              | 1 | 1 | 0          | 0      | Х7   |  |

| 2              | 1 | 1 | 1          | 0      | 0    |  |

| 2              | 2 | 2 | 2          | 1      | Hi-Z |  |

2 = Don't care

Hi-Z = 3-STATE condition Xn = Data at input n

© 1999 Fairchild Semiconductor Corporation DS005993.prf

## Absolute Maximum Ratings(Note 1)

(Note 2)

## **Recommended Operating** Conditions (Note 2)

| -0.5 to $+18$ V <sub>DC</sub>     |

|-----------------------------------|

| $-0.5$ to $V_{DD} + 0.5 \ V_{DC}$ |

| -65°C to +150°C                   |

|                                   |

| 700 mW                            |

| 500 mW                            |

|                                   |

| 260°C                             |

|                                   |

DC Electrical Characteristics (Note 2)

DC Supply Voltage (V DD) Input Voltage (VIN)

0 to V<sub>DD</sub> V<sub>DC</sub>

3.0 to 15 V<sub>DC</sub>

$-40^{\circ}C$  to  $+85^{\circ}C$ Operating Temperature Range (T<sub>A</sub>) Note 1: "Absolute Maximum Ratings" are those values beyond which the

safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The Recommended

#### N V Operating Conditions and Electrical Characteristics table provide conditions for actual device operation. Note 2: $V_{SS} = 0V$ unless otherwise specified.

#### -40°C +25°C +85°C Conditions Symbol Parameter Units Min Max Max Min Тур Max Min $V_{DD} = 5V$ , $V_{IN} = V_{DD}$ or $V_{SS}$ IDD Quiescent Device 20 0.005 20 150 μA Current $V_{DD} = 10V, V_{IN} = V_{DD} \text{ or } V_{SS}$ 40 0.010 40 300 μΑ $V_{DD} = 15V, V_{IN} = V_{DD} \text{ or } V_{SS}$ 80 0.015 80 600 μΑ VOL LOW Level $V_{DD} = 5V$ 0.05 0 0.05 0.05 V Output Voltage $V_{DD} = 10V$ $|I_{OL}| < 1 \ \mu A$ 0.05 0 0.05 0.05 V $V_{DD} = 15V$ 0.05 0 0.05 0.05 V HIGH Level $V_{DD} = 5V$ V Vон 4.95 4.95 5.0 4.95 Output Voltage $V_{DD} = 10V$ $|I_{OH}| < 1 \ \mu A$ 9.95 9.95 10.0 9.95 V $V_{DD} = 15V$ 14.95 14.95 15.0 14.95 V VIL LOW Level $V_{DD}=5V,\,V_O=0.5V$ 1.5 2.25 1.5 1.5 V v Input Voltage $V_{DD} = 10V, V_{O} = 1.0V$ 3.0 4.50 3.0 3.0 V<sub>DD</sub> = 15V, V<sub>O</sub> = 1.5V 4.0 6.75 4.0 4.0 V $V_{DD} = 5V, V_{O} = 4.5V$ VIH HIGH Level 3.5 3.5 2.75 3.5 ٧ Input Voltage $V_{DD} = 10V, V_{O} = 9.0V$ 7.0 7.0 v 7.0 5.50 $V_{DD} = 15V, V_O = 13.5V$ 11.0 11.0 8.25 11.0 V LOW Level Output $V_{DD} = 5V, V_{O} = 0.4V$ loL 0.52 0.44 0.78 0.36 mΑ Current $V_{DD} = 10V, V_{O} = 0.5V$ 1.3 1.1 2.0 0.9 mΑ (Note 3) $V_{DD} = 15V, V_{O} = 1.5V$ 3.6 3.4 7.8 2.4 mΑ HIGH Level Output $V_{DD} = 5V, V_O = 4.6V$ -0.2 -0.12 I<sub>OH</sub> -0.16 mΑ V<sub>DD</sub> = 10V, V<sub>O</sub> = 9.5 Current -0.5 -0.4 -0.3 mΑ (Note 3) V<sub>DD</sub> = 15V, V<sub>O</sub> = 13.5V -1.4 -1.2 -1.0 mA Input Current $V_{DD} = 15V, V_{IN} = 0V$ IIN -0.3 -10 -0.3 -1.0 μΑ 10<sup>-5</sup> $V_{DD} = 15V, V_{IN} = 15V$ 0.3 0.3 1.0 μΑ 3-STATE $V_{DD} = 15V, V_{O} = 0V$ ±1.0 $+10^{-1}$ ±1.0 +7.5loz μΑ $V_{DD} = 15V, V_O = 15V$ Output Current

Note 3: I<sub>OH</sub> and I<sub>OL</sub> are tested one output at a time

CD4512BC

| S |

|---|

| ш |

| 2 |

| 5 |

| ņ |

| 4 |

| Δ |

| C |

|   |

## AC Electrical Characteristics (Note 4)

| Symbol                                | Parameter                  | Conditions     | (   | CD4512BM |     |     | CD4512BC |     |       |

|---------------------------------------|----------------------------|----------------|-----|----------|-----|-----|----------|-----|-------|

| Symbol                                |                            |                | Min | Тур      | Max | Min | Тур      | Max | Units |

| t <sub>PHL</sub>                      | Propagation Delay          | $V_{DD} = 5V$  |     | 225      | 500 |     | 225      | 750 | ns    |

|                                       | HIGH-to-LOW Level          | $V_{DD} = 10V$ |     | 75       | 175 |     | 75       | 200 | ns    |

|                                       |                            | $V_{DD} = 15V$ |     | 57       | 130 |     | 57       | 150 | ns    |

|                                       | Propagation Delay          | $V_{DD} = 5V$  |     | 225      | 500 |     | 225      | 750 | ns    |

|                                       | LOW-to-HIGH Level          | $V_{DD} = 10V$ |     | 75       | 175 |     | 75       | 200 | ns    |

|                                       |                            | $V_{DD} = 15V$ |     | 57       | 130 |     | 57       | 150 | ns    |

| t <sub>THL</sub> , t <sub>TLH</sub> T | Transition Time            | $V_{DD} = 5V$  |     | 70       | 200 |     | 70       | 200 | ns    |

|                                       |                            | $V_{DD} = 10V$ |     | 35       | 100 |     | 35       | 100 | ns    |

|                                       |                            | $V_{DD} = 15V$ |     | 25       | 80  |     | 25       | 80  | ns    |

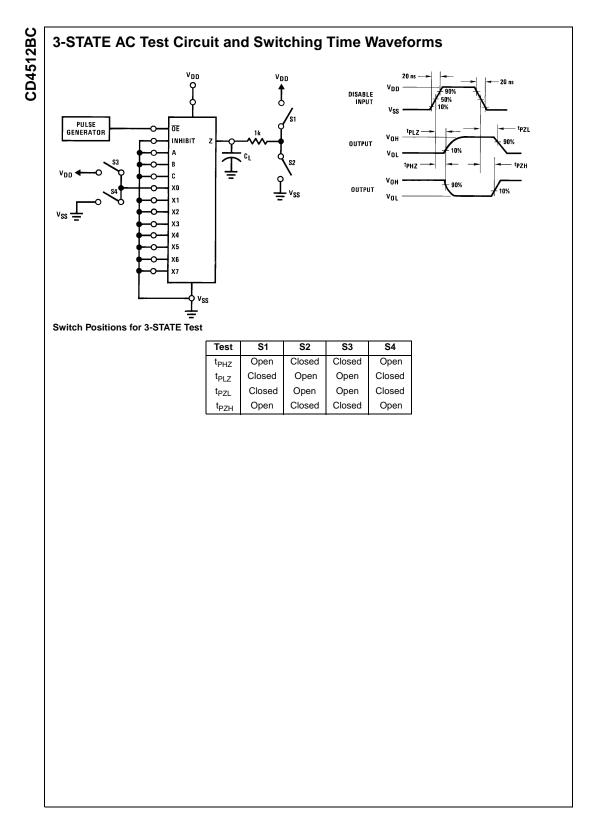

|                                       | Propagation Delay into     | $V_{DD} = 5V$  |     | 50       | 125 |     | 50       | 125 | ns    |

|                                       | 3-STATE from Logic Level   | $V_{DD} = 10V$ |     | 25       | 75  |     | 25       | 75  | ns    |

|                                       |                            | $V_{DD} = 15V$ |     | 19       | 60  |     | 19       | 60  | ns    |

| t <sub>PZH</sub> , t <sub>PZL</sub>   | Propagation Delay to Logic | $V_{DD} = 5V$  |     | 50       | 125 |     | 50       | 125 | ns    |

|                                       | Level from 3-STATE         | $V_{DD} = 10V$ |     | 25       | 75  |     | 25       | 75  | ns    |

|                                       |                            | $V_{DD} = 15V$ |     | 19       | 60  |     | 19       | 60  | ns    |

| C <sub>IN</sub>                       | Input Capacitance          | (Note 5)       |     | 7.5      | 15  |     | 7.5      | 15  | pF    |

| C <sub>OUT</sub>                      | 3-STATE Output             | (Note 5)       |     | 7.5      | 15  |     | 7.5      | 15  | pF    |

|                                       | Capacitance                |                |     |          |     |     |          |     |       |

| C <sub>PD</sub>                       | Power Dissipation Capacity | (Note 6)       |     | 150      |     |     | 150      |     | pF    |

Note 4: AC Parameters are guaranteed by DC correlated testing.

Note 5: Capacitance guaranteed by periodic testing.

Note 6: C<sub>PD</sub> determines the no load AC power of any CMOS device. For complete explanation, see Family Characteristics Application Note, AN-90.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.