FAIRCHILD

SEMICONDUCTOR

October 1987 Revised July 1999

# CD40174BC • CD40175BC Hex D-Type Flip-Flop • Quad D-Type Flip-Flop

# **General Description**

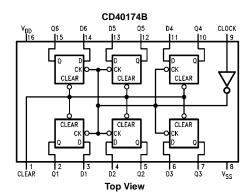

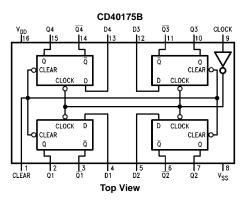

The CD40174BC consists of six positive-edge triggered Dtype flip-flops; the true outputs from each flip-flop are externally available. The CD40175BC consists of four positiveedge triggered D-type flip-flops; both the true and complement outputs from each flip-flop are externally available.

All flip-flops are controlled by a common clock and a common clear. Information at the D inputs meeting the set-up time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse. The clearing operation, enabled by a negative <u>p</u>ulse at Clear input, clears all Q outputs to logical "0" and Q s (CD40175BC only) to logical "1".

All inputs are protected from static discharge by diode clamps to  $V_{DD}$  and  $V_{SS}.$

## **Features**

- Wide supply voltage range: 3V to 15V

- High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- Low power TTL compatibility:

- fan out of 2 driving 74L or 1 driving 74 LS ■ Equivalent to MC14174B, MC14175B

- Equivalent to MM74C174, MM74C175

# **Ordering Code:**

| 00404740014 |      |                                                                                   |

|-------------|------|-----------------------------------------------------------------------------------|

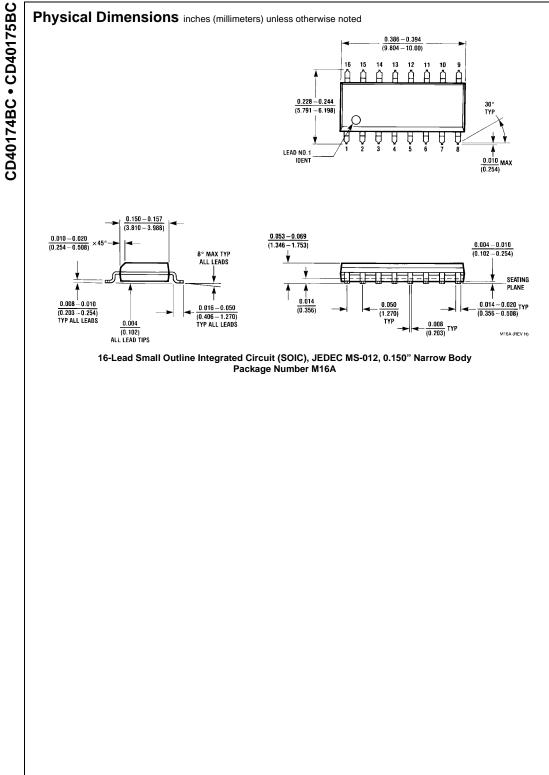

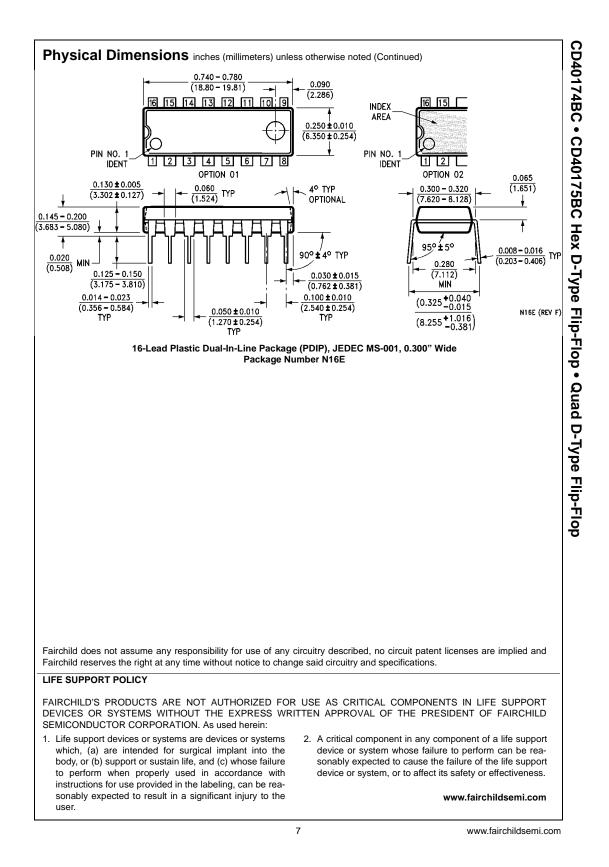

| CD40174BCM  | M16A | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |

| CD40174BCN  | N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |

| CD40175BCM  | M16A | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |

| CD40175BCN  | N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

# **Connection Diagrams**

## Pin Assignments for DIP and SOIC

© 1999 Fairchild Semiconductor Corporation DS005987

# CD40174BC • CD40175BC

| Inputs |            |   | Outputs |               |  |

|--------|------------|---|---------|---------------|--|

| Clear  | Clock      | D | Q       | Q<br>(Note 1) |  |

| L      | Х          | Х | L       | н             |  |

| н      | $\uparrow$ | н | н       | L             |  |

| н      | $\uparrow$ | L | L       | н             |  |

| н      | н          | х | NC      | NC            |  |

| н      | L          | х | NC      | NC            |  |

H = HIGH Level L = LOW Level X = Irrelevant ↑ = Transition from LOW-to-HIGH level NC = No change

Note 1:  $\overline{Q}$  for CD40175B only

Truth Table

# Absolute Maximum Ratings(Note 2)

|                                      | <b>U</b> (                        |

|--------------------------------------|-----------------------------------|

| (Note 3)                             |                                   |

| DC Supply Voltage (V <sub>DD</sub> ) | -0.5V to +18V                     |

| Input Voltage (V <sub>IN</sub> )     | –0.5V to $V_{DD}$ +0.5V $_{DC}$   |

| Storage Temperature Range $(T_S)$    | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Power Dissipation (P <sub>D</sub> )  |                                   |

| Dual-In-Line                         | 700 mW                            |

| Small Outline                        | 500 mW                            |

| Lead Temperature (T <sub>L</sub> )   |                                   |

| (Soldering, 10 seconds)              | 260°C                             |

|                                      |                                   |

# Recommended Operating Conditions (Note 3)

| DC Supply Voltage (V <sub>DD</sub> )                                                               | 3V to 15 $V_{DC}$                |

|----------------------------------------------------------------------------------------------------|----------------------------------|

| Input Voltage (V <sub>IN</sub> )                                                                   | 0V to $V_{DD} V_{DC}$            |

| Operating Temperature Range (T <sub>A</sub> )                                                      | $-40^{\circ}C$ to $+85^{\circ}C$ |

| Note 2: "Absolute Maximum Ratings" are those va<br>safety of the device cannot be guaranteed. They | are not meant to imply           |

| that the devices should be operated at these limits.                                               | The tables of "Recom-            |

that the devices should be operated at these limits. The tables of "Recommended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation. **Note 3:**  $V_{SS} = 0V$  unless otherwise specified.

# DC Electrical Characteristics (Note 3)

| Symbol          | Parameter         | Conditions                                        | -40   | <b>−40°C</b> |       | +25°C             |       |       | +85°C |                   |

|-----------------|-------------------|---------------------------------------------------|-------|--------------|-------|-------------------|-------|-------|-------|-------------------|

| Symbol          | Parameter         | Conditions                                        | Min   | Max          | Min   | Тур               | Max   | Min   | Мах   | Units             |

| I <sub>DD</sub> | Quiescent Device  | $V_{DD} = 5V, V_{IN} = V_{DD} \text{ or } V_{SS}$ |       | 4            |       |                   | 4     |       | 30    | μA                |

|                 | Current           | $V_{DD}$ = 10V, $V_{IN}$ = $V_{DD}$ or $V_{SS}$   |       | 8            |       |                   | 8     |       | 60    | μA                |

|                 |                   | $V_{DD}$ = 15V, $V_{IN}$ = $V_{DD}$ or $V_{SS}$   |       | 16           |       |                   | 16    |       | 120   | μA                |

| V <sub>OL</sub> | LOW Level         | $V_{DD} = 5V$                                     |       | 0.05         |       |                   | 0.05  |       | 0.05  | V                 |

|                 | Output Voltage    | $V_{DD} = 10V$                                    |       | 0.05         |       |                   | 0.05  |       | 0.05  | V                 |

|                 |                   | $V_{DD} = 15V$                                    |       | 0.05         |       |                   | 0.05  |       | 0.05  | V                 |

| V <sub>ОН</sub> | HIGH Level        | $V_{DD} = 5V$                                     | 4.95  |              | 4.95  | 5                 |       | 4.95  |       | V                 |

|                 | Output Voltage    | $V_{DD} = 10V$                                    | 9.95  |              | 9.95  | 10                |       | 9.95  |       | V                 |

|                 |                   | $V_{DD} = 15V$                                    | 14.95 |              | 14.95 | 15                |       | 14.95 |       | V                 |

| V <sub>IL</sub> | LOW Level         | $V_{DD} = 5V, V_{O} = 0.5V \text{ or } 4.5V$      |       | 1.5          |       |                   | 1.5   |       | 1.5   | 5 V<br>0 V<br>0 V |

|                 | Input Voltage     | $V_{DD} = 10V, V_O = 1V \text{ or } 9V$           |       | 3.0          |       |                   | 3.0   |       | 3.0   | V                 |

|                 |                   | $V_{DD} = 15V$ , $V_O = 1.5V$ or $13.5V$          |       | 4.0          |       |                   | 4.0   |       | 4.0   | V                 |

| VIH             | HIGH Level        | $V_{DD} = 5V, V_{O} = 0.5V \text{ or } 4.5V$      | 3.5   |              | 3.5   |                   |       | 3.5   |       | V                 |

|                 | Input Voltage     | $V_{DD} = 10V, V_O = 1V \text{ or } 9V$           | 7.0   |              | 7.0   |                   |       | 7.0   |       | V                 |

|                 |                   | $V_{DD} = 15V$ , $V_O = 1.5V$ or $13.5V$          | 11.0  |              | 11.0  |                   |       | 11.0  |       | V                 |

| I <sub>OL</sub> | LOW Level Output  | $V_{DD} = 5V, V_{O} = 0.4V$                       | 0.52  |              | 0.44  | 0.88              |       | 0.36  |       | mA                |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_{O} = 0.5V$                      | 1.3   |              | 1.1   | 2.25              |       | 0.9   |       | mA                |

|                 |                   | $V_{DD} = 15V, V_{O} = 1.5V$                      | 3.6   |              | 3.0   | 8.8               |       | 2.4   |       | mA                |

| I <sub>OH</sub> | HIGH Level Output | $V_{DD} = 5V, V_{O} = 4.6V$                       | -0.52 |              | -0.44 | -0.88             |       | -0.36 |       | mA                |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_{O} = 9.5V$                      | -1.3  |              | -1.1  | -2.25             |       | -0.9  |       | mA                |

|                 |                   | $V_{DD} = 15V, V_{O} = 13.5V$                     | -3.6  |              | -3.0  | -8.8              |       | -2.4  |       | mA                |

| I <sub>IN</sub> | Input Current     | $V_{DD} = 15V, V_{IN} = 0V$                       |       | -0.30        |       | -10 <sup>-5</sup> | -0.30 |       | -1.0  | mA<br>mA<br>mA    |

|                 |                   | V <sub>DD</sub> = 15V, V <sub>IN</sub> = 15V      |       | 0.30         |       | 10 <sup>-5</sup>  | 0.30  |       | 1.0   | μA                |

Note 4:  $I_{\mbox{OH}}$  and  $I_{\mbox{OL}}$  are tested one output at a time.

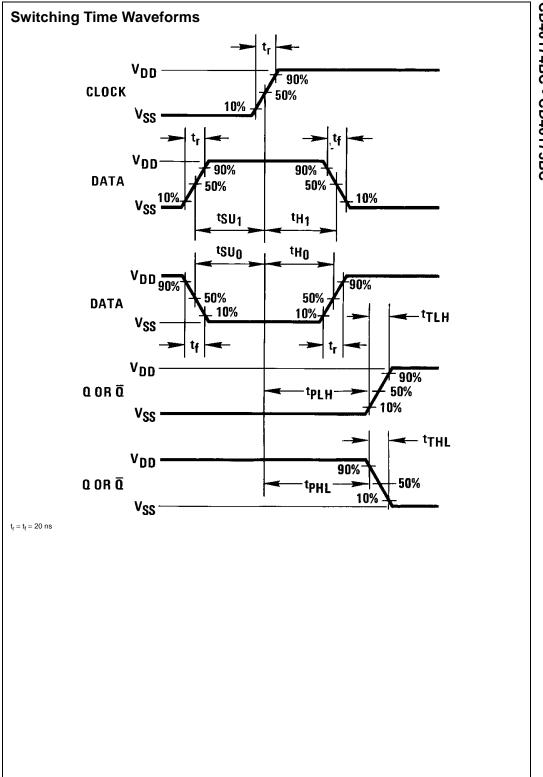

| $T_{\rm A} = 25  0,  0_{\rm L}$     | = 50 pF, $R_L$ = 200k and $t_r$ = $t_f$ = 20 ns, unl | eas otherwise specified |     |     |     |      |

|-------------------------------------|------------------------------------------------------|-------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                                            | Conditions              | Min | Тур | Max | Unit |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time to a                          | $V_{DD} = 5V$           |     | 190 | 300 | ns   |

|                                     | Logical "0" or Logical "1" from                      | $V_{DD} = 10V$          |     | 75  | 110 | ns   |

|                                     | Clock to Q or Q (CD40175 Only)                       | $V_{DD} = 15V$          |     | 60  | 90  | ns   |

| t <sub>PHL</sub>                    | Propagation Delay Time to a                          | $V_{DD} = 5V$           |     | 180 | 300 | ns   |

|                                     | Logical "0" from Clear to Q                          | $V_{DD} = 10V$          |     | 70  | 110 | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 60  | 90  | ns   |

| t <sub>PLH</sub>                    | Propagation Delay Time to a Logical                  | $V_{DD} = 5V$           |     | 230 | 400 | ns   |

|                                     | "1" from Clear to Q (CD40175 Only)                   | $V_{DD} = 10V$          |     | 90  | 150 | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 75  | 120 | ns   |

| t <sub>SU</sub>                     | Time Prior to Clock Pulse that                       | $V_{DD} = 5V$           |     | 45  | 100 | ns   |

|                                     | Data must be Present                                 | $V_{DD} = 10V$          |     | 15  | 40  | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 13  | 35  | ns   |

| t <sub>H</sub>                      | Time after Clock Pulse that                          | $V_{DD} = 5V$           |     | -11 | 0   | ns   |

|                                     | Data Must be Held                                    | $V_{DD} = 10V$          |     | -4  | 0   | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | -3  | 0   | ns   |

| t <sub>THL</sub> , t <sub>TLH</sub> | Transition Time                                      | $V_{DD} = 5V$           |     | 100 | 200 | ns   |

|                                     |                                                      | $V_{DD} = 10V$          |     | 50  | 100 | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 40  | 80  | ns   |

| t <sub>WH</sub> , t <sub>WL</sub>   | Minimum Clock Pulse Width                            | $V_{DD} = 5V$           |     | 130 | 250 | ns   |

|                                     |                                                      | $V_{DD} = 10V$          |     | 45  | 100 | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 40  | 80  | ns   |

| t <sub>WL</sub>                     | Minimum Clear Pulse Width                            | $V_{DD} = 5V$           |     | 120 | 250 | ns   |

|                                     |                                                      | $V_{DD} = 10V$          |     | 45  | 100 | ns   |

|                                     |                                                      | $V_{DD} = 15V$          |     | 40  | 80  | ns   |

| t <sub>RCL</sub>                    | Maximum Clock Rise Time                              | $V_{DD} = 5V$           | 15  |     |     | μs   |

|                                     |                                                      | $V_{DD} = 10V$          | 5.0 |     |     | μs   |

|                                     |                                                      | $V_{DD} = 15V$          | 5.0 |     |     | μs   |

| t <sub>fCL</sub>                    | Maximum Clock Fall Time                              | $V_{DD} = 5V$           | 15  | 50  |     | μs   |

|                                     |                                                      | $V_{DD} = 10V$          | 5.0 | 50  |     | μs   |

|                                     |                                                      | $V_{DD} = 15V$          | 5.0 | 50  |     | μs   |

| f <sub>CL</sub>                     | Maximum Clock Frequency                              | $V_{DD} = 5V$           | 2.0 | 3.5 |     | MH   |

|                                     |                                                      | $V_{DD} = 10V$          | 5.0 | 10  |     | MH   |

|                                     |                                                      | $V_{DD} = 15V$          | 6.0 | 12  |     | MH   |

| C <sub>IN</sub>                     | Input Capacitance                                    | Clear Input             |     | 10  | 15  | pF   |

|                                     |                                                      | Other Input             |     | 5.0 | 7.5 | pF   |

| C <sub>PD</sub>                     | Power Dissipation                                    | Per Package (Note 6)    |     | 130 |     |      |

|                                     |                                                      |                         |     |     |     |      |

Note 5: AC Parameters are guaranteed by DC correlated testing.

Note 6: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation, see 74C Family Characteristics application note, AN-90.

CD40174BC • CD40175BC